details

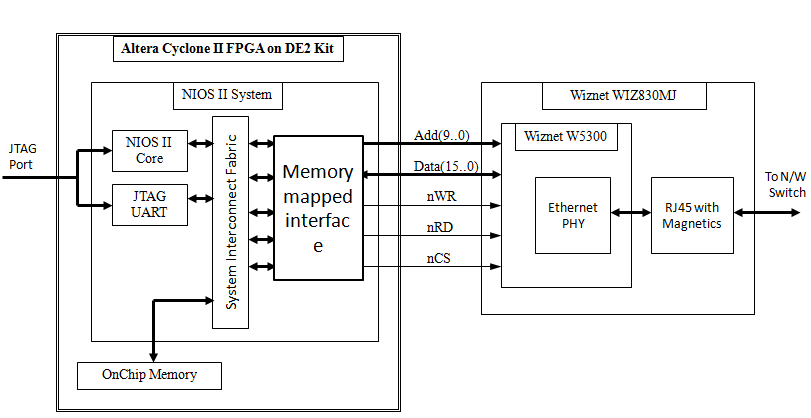

This report shows then performance of Wiznet Ethernet chip W5300 used FPGA user board which has embedded processor NIOS-II in FPGA. this is block diagram of test environment.  shortly, the report says the result as follows :

shortly, the report says the result as follows :

| 50 MHz NIOSII clk frequency | TCP | UDP |

| Data Rate | 10.3 Mbps | 10.27Mbps |

| Data reliability | All the bytes sent are received at the destination correctly. | While using wiznet as UDP server approx 5% of data loss is observed due to mismatch in PC processor and NIOSII processor speed. |

SOURCE:www.hecr.tifr.res.in (localcopy : W5300_report)

COMMENTS